1、单选题:

计算机系统的五大部件之间两种互联方式为___

选项:

A: 总线连接和分散连接

B: 分散连接和聚集连接

C: 总线连接和聚集连接

D: 分散连接和芯片连接

答案: 【 总线连接和分散连接】

2、单选题:

按连接部件不同可以对总线分为三大类,其中不属于这三类的是___

选项:

A: 存储总线

B: 片内总线

C: 系统总线

D: 通信总线

答案: 【 存储总线 】

3、单选题:

下列不属于系统总线的为___

选项:

A: 片内总线

B: 数据总线

C: 地址总线

D: 控制总线

答案: 【 片内总线】

4、单选题:

相对于单总线结构,多总线结构解决了___速度不匹配的问题。

选项:

A: CPU、主存与I/O设备间

B: 地址总线与数据总线

C: 寄存器与ALU

D: I/O设备间

答案: 【 CPU、主存与I/O设备间】

5、单选题:

DMA总线用于___之间交换信息

选项:

A: 主存与I/O设备

B: CPU与主存

C: CPU与I/O设备

D: I/O设备间

答案: 【 主存与I/O设备】

6、单选题:

下列不属于集中控制优先权仲裁方式的为___

选项:

A: 同步查询

B: 链式查询

C: 计时器定时查询

D: 独立请求方式

答案: 【 同步查询】

7、单选题:

总线通信控制的四种方式不包括___

选项:

A: DMA通信

B: 同步通信

C: 异步通信

D: 半同步通信

答案: 【 DMA通信】

8、单选题:

下列不属于片内总线连接的是___

选项:

A: CPU与内存间

B: 寄存器与寄存器间

C: 寄存器与算逻单元之间

D: CPU芯片内部

答案: 【 CPU与内存间】

9、单选题:

在计算机的总线中,不同信号在同一条信号线上分时传输的方式称为___

选项:

A: 总线复用

B: 并行传输

C: 串行传输

D: 并行或串行传输

答案: 【 总线复用】

10、单选题:

总线是连接多个模块的信息传输线,是各部件共享的传输介质。因此在某一时刻允许有___个部件向总线发送信息。

选项:

A: 一个

B: 两个

C: 三个

D: 多个

答案: 【 一个】

11、单选题:

衡量总线本身所能达到最高传输速率的重要指标是___

选项:

A: 总线带宽

B: 总线宽度

C: 总线复用

D: 信号线数

答案: 【 总线带宽】

12、单选题:

连接CPU内各寄存器、控制器及算数逻辑运算单元等部件的总线统称为___

选项:

A: 片内总线

B: 系统总线

C: 数据总线

D: 控制总线

答案: 【 片内总线】

13、单选题:

“BS:总线忙”信号的建立者是___

选项:

A: 获得总线控制权的设备

B: 发起总线请求的设备

C: 总线控制器

D: CPU

答案: 【 获得总线控制权的设备】

14、单选题:

在计数器定时查询方式下,若每次计数都是从0开始,则___

选项:

A: 设备号越小优先级越高

B: 每个设备的优先级相同

C: 设备号越大优先级越高

D: 无法确定设备优先级

答案: 【 设备号越小优先级越高】

15、单选题:

以下几种总线判优控制方式中,响应速度快,优先次序控制灵活,但控制线数量多,总线控制更为复杂的是___

选项:

A: 独立请求方式

B: 链式查询方式

C: 计时器定时查询方式

D: 都可以

答案: 【 独立请求方式】

16、单选题:

假设某系统总线在一个总线周期中并行传输8字节信息,一个总线周期占用4个时钟周期,总线时钟频率为10MHz,则总线带宽是___

选项:

A: 20MB/s

B: 10MB/s

C: 30MB/s

D: 40MB/s

答案: 【 20MB/s】

17、单选题:

在三种集中式总线控制中, 方式对电路故障最敏感。

选项:

A: 链式查询

B: 计数器式定时查询

C: 独立请求

D: 都一样

答案: 【 链式查询】

18、单选题:

在三种集中式总线控制中, 方式反应最快。

选项:

A: 独立请求

B: 链式查询

C: 计数器式定时查询

D: 都一样

答案: 【 独立请求】

19、单选题:

在各种异步通信方式中, 速度最快。

选项:

A: 不互锁

B: 全互锁

C: 半互锁

D: 都一样

答案: 【 不互锁】

20、单选题:

总线的异步通信方式是 。

选项:

A: 不采用时钟信号,只采用握手信号

B: 不采用时钟信号,不采用握手信号

C: 只采用时钟信号,不采用握手信号

D: 即采用时钟信号,又采用握手信号

答案: 【 不采用时钟信号,只采用握手信号】

21、单选题:

在异步串行传输系统中,假设每秒传输120个数据帧,其字符格式规定包含1个起始位,7个数据位,1个奇偶校验位,1个终止位,则波特率为___。

选项:

A: 1200bps

B: 800bps

C: 600bps

D: 900bps

答案: 【 1200bps】

22、单选题:

在异步传输系统中,若字符格式为:1位起始位、8位数据位、1位奇偶校验位、1位终止位,假设波特率为1200bps,则比特率为 .

选项:

A: 872.72bps

B: 1200bps

C: 981.81bps

D: 1320bps

答案: 【 872.72bps】

23、单选题:

总线复用方式可以___。

选项:

A: 减少总线中信号线的数量

B: 提高总线的传输带宽

C: 增加总线的功能

D: 实现并行传输

答案: 【 减少总线中信号线的数量】

24、单选题:

在同步通信中,一个总线周期的传输过程是___。

选项:

A: 先传输地址,再传输数据

B: 先传输数据,再传输地址

C: 只传输数据

D: 只传输地址

答案: 【 先传输地址,再传输数据】

25、单选题:

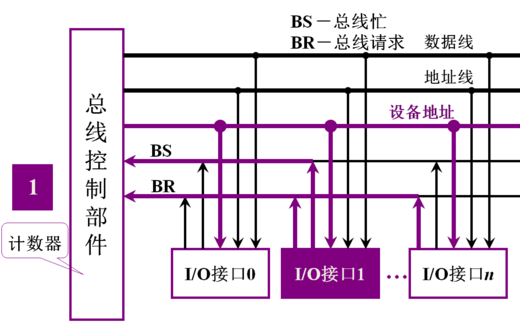

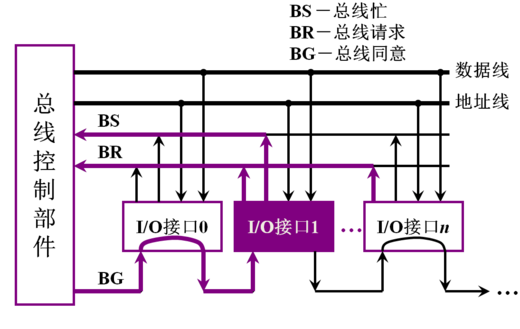

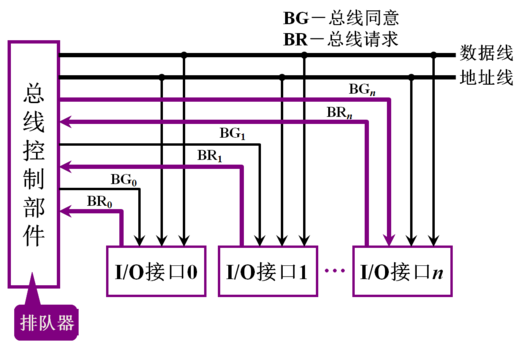

总线上连接着各类设备,按其对总线有无控制能力可分为主设备和从设备两种。若多个主设备同时要使用总线时,就由总线控制器的判优、仲裁逻辑按照一定的优先等级顺序确定哪个主设备能使用总线。

总线判优控制可分集中式和分布式两种,常见的集中控制优先权仲裁方式有三种:链式查询方式、计数器定时查询、独立请求方式。以下为______总线判优方式的接线图:

选项:

A: 计数器定时查询

B: 链式查询方式

C: 独立请求方式

D: 某种分布式判优

答案: 【 计数器定时查询】

26、单选题:

总线上连接着各类设备,按其对总线有无控制能力可分为主设备和从设备两种。若多个主设备同时要使用总线时,就由总线控制器的判优、仲裁逻辑按照一定的优先等级顺序确定哪个主设备能使用总线。

总线判优控制可分集中式和分布式两种,常见的集中控制优先权仲裁方式有三种:链式查询方式、计数器定时查询、独立请求方式。以下为______总线判优方式的接线图:

选项:

A: 链式查询方式

B: 计数器定时查询

C: 独立请求方式

D: 某种分布式判优

答案: 【 链式查询方式】

27、单选题:

总线上连接着各类设备,按其对总线有无控制能力可分为主设备和从设备两种。若多个主设备同时要使用总线时,就由总线控制器的判优、仲裁逻辑按照一定的优先等级顺序确定哪个主设备能使用总线。

总线判优控制可分集中式和分布式两种,常见的集中控制优先权仲裁方式有三种:链式查询方式、计数器定时查询、独立请求方式。以下为______总线判优方式的接线图:

选项:

A: 独立请求方式

B: 链式查询方式

C: 某种分布式判优

D: 计数器定时查询

答案: 【 独立请求方式】

28、单选题:

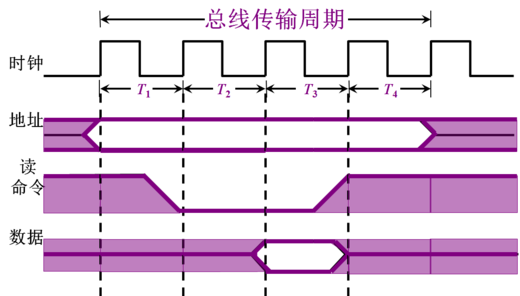

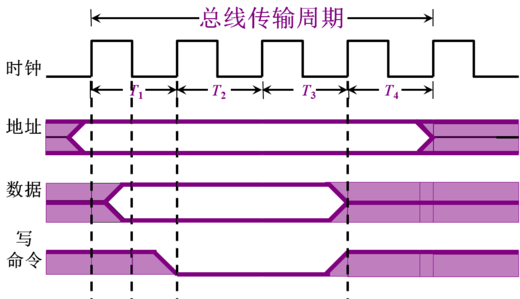

总线通信控制主要解决通信双方如何获知传输开始和传输结束,以及通信双方如何协调如何配合。

通常有四种方式:同步通信、异步通信、半同步通信和分离式通信。

同步通信中,通信双方由统一时标控制数据传送。下图表示了某输入设备向CPU传输数据的同步通信过程。

图中总线传输周期是连接在总线上的两个部件完成一次完整且可靠地信息传输时间,它包含4个时钟周期T1 、T2 、T3 、T4 。在上图所示读命令中,T3时钟周期执行的操作是____

选项:

A: 从模块提供数据

B: 主模块发出地址

C: 主模块发读命令

D: 主模块撤销读命令,从模块撤销数据

答案: 【 从模块提供数据】

29、单选题:

总线通信控制主要解决通信双方如何获知传输开始和传输结束,以及通信双方如何协调如何配合。

通常有四种方式:同步通信、异步通信、半同步通信和分离式通信。

同步通信中,通信双方由统一时标控制数据传送。下图表示了CPU向某输设备传输数据的同步通信过程。

图中总线传输周期是连接在总线上的两个部件完成一次完整且可靠地信息传输时间,对于写命令,它包含时钟周期T1 、T1.5 、T2 、T3和T4 。在上图所示写命令中,T2时钟周期执行的操作是____

选项:

A: 主模块发出写命令,从模块接收到命令后,必须在规定时间内将数据总线上的数据写到地址总线所指明的单元中。

B: 主模块发出地址

C: 主模块提供数据

D: 主模块撤销读命令,从模块撤销数据

答案: 【 主模块发出写命令,从模块接收到命令后,必须在规定时间内将数据总线上的数据写到地址总线所指明的单元中。】

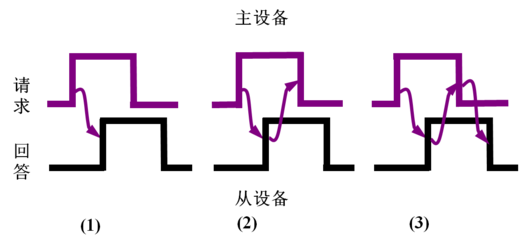

30、单选题:

总线通信控制主要解决通信双方如何获知传输开始和传输结束,以及通信双方如何协调如何配合。通常有四种方式:同步通信、异步通信、半同步通信和分离式通信。在异步通信中,应答方式又可分为不互锁、半互锁和全互锁三种类型。下图表示了异步通信中请求与应答的互锁关系,下列说法正确的是____

选项:

A: (1)是不互锁 (2)是半互锁 (3)是全互锁

B: (1)是半互锁 (2)是不互锁 (3)是全互锁

C: (1)是全互锁 (2)是不互锁 (3)是是半互锁

D: (1)是不互锁 (2)是全互锁 (3)是半互锁

答案: 【 (1)是不互锁 (2)是半互锁 (3)是全互锁】

31、单选题:

通常将完成一次总线操作的时间称为总线周期,可以分为4个阶段。1)申请分配阶段。2)寻址阶段 3)传数阶段4)结束阶段,一个总线周期各阶段执行的优先次序是___

选项:

A: 申请分配阶段à寻址阶段à传数阶段-à结束阶段

B: 寻址阶段à申请分配阶段à传数阶段-à结束阶段

C: 申请分配阶段à传数阶段à寻址阶段-à结束阶段

D: 寻址阶段à申请分配阶段à传数阶段-à结束阶段

答案: 【 申请分配阶段à寻址阶段à传数阶段-à结束阶段】

32、单选题:

总线宽度又成总线位宽,它是总线上同时能够传输的数据位数,通常是指____的根数

选项:

A: 数据总线

B: 控制总线

C: 地址总线

D: 数据总线+控制总线+地址总线

答案: 【 数据总线】

33、多选题:

总线特性包括___

选项:

A: 机械特性

B: 电气特性

C: 功能特性

D: 时间特性

E: 信号特性

F: 控制特性

答案: 【 机械特性 ;

电气特性;

功能特性;

时间特性 】

34、多选题:

系统总线是连接计算机内各大部件的信息传输线,该总线按传输内容的不同又分为___

选项:

A: 数据总线

B: 地址总线

C: 控制总线

D: 存储总线

E: 传输总线

答案: 【 数据总线;

地址总线;

控制总线】

35、多选题:

下列选项中的英文缩写均为总线标准的是___

选项:

A: PCI

B: USB

C: ISA

D: CPI

E: MIPS

答案: 【 PCI;

USB;

ISA】

36、多选题:

.所谓的三总线结构的计算机中的“三总线”包含 。

选项:

A: I/O总线

B: 主存总线

C: DMA总线

D: 地址线

E: 数据线

F: 控制线

答案: 【 I/O总线 ;

主存总线;

DMA总线】

37、多选题:

按连接部件不同,总线通常可分为以下哪些种 。

选项:

A: 片内总线

B: 系统总线

C: 通信总线

D: 控制线

E: 地址线

F: 主存总线

答案: 【 片内总线;

系统总线;

通信总线】

38、多选题:

一个总线传输周期包括____几个阶段

选项:

A: 申请分配阶段

B: 寻址阶段

C: 传输阶段

D: 结束阶段

E: 握手阶段

答案: 【 申请分配阶段;

寻址阶段;

传输阶段;

结束阶段】

39、多选题:

总线标准可视为系统与各模块、模块与模块之间的一个互连的界面标准。这个界面对其它两端的模块都是透明的。下列常用的各种标准中,属于总线标准的是______

选项:

A: ISA

B: PCI

C: EISA

D: VESA

E: IEEE 802

答案: 【 ISA;

PCI;

EISA;

VESA】

40、多选题:

控制总线中常见的控制信号包括___

选项:

A: 时钟

B: 复位

C: 存储器写

D: 总线请求

E: 中断请求

F: 传输响应

答案: 【 时钟;

复位;

存储器写;

总线请求;

中断请求;

传输响应】

1、单选题:

___层次主要解决了CPU和主存速度不匹配的问题。

选项:

A: 缓存-主存

B: 主存-辅存

C: CPU-辅存

D: 无正确答案

答案: 【 缓存-主存】

2、单选题:

从用户角度,存储器的主要性能指标不包括___。

选项:

A: 存取方式

B: 速度

C: 容量

D: 每位价格

答案: 【 存取方式】

3、单选题:

存储字长都取___。

选项:

A: 8的倍数

B: 8

C: 2 的倍数(如2,4,6…)

D: 无限制

答案: 【 8的倍数】

4、单选题:

半导体存储芯片的译码驱动方式有两种___

选项:

A: 线选法和重合法

B: 线选法和片选法

C: 片选法和重合法

D: 线选法和复用法

答案: 【 线选法和重合法】

5、单选题:

某一静态RAM芯片,其容量为1K×4位,除电源和接地端外,该芯片引出线的最少数目为:

选项:

A: 14

B: 16

C: 10

D: 12

答案: 【 16】

6、单选题:

动态RAM常用的三种刷新方式中不包括

选项:

A: 静态刷新

B: 集中刷新

C: 分散刷新

D: 异步刷新

答案: 【 静态刷新】

7、单选题:

下列说法错误的是___

选项:

A: 动态RAM比静态RAM速度高

B: 动态RAM需要再生,故需配置再生电路

C: 动态RAM的功耗比静态RAM小

D: 动态RAM的价格比静态RAM的价格便宜

答案: 【 动态RAM比静态RAM速度高】

8、单选题:

下列说法错误的是

选项:

A: 动态RAM的集成度低于静态RAM的集成度

B: 动态RAM行、列地址按先后顺序输送,减少了芯片引脚,封装尺寸也减少

C: 动态RAM的速度比静态RAM的速度低

D: 静态RAM的价格比动态RAM的价格高

答案: 【 动态RAM的集成度低于静态RAM的集成度】

9、单选题:

下列存储器中,CPU不能直接访问的是___

选项:

A: 硬盘

B: Cache

C: 寄存器

D: RAM

答案: 【 硬盘】

10、单选题:

以下存储器构成的体系结构中,存储器存取速度由慢到快的排列顺序是___

选项:

A: 辅存—主存—Cache—寄存器

B: 主存—辅存—Cache—寄存器

C: 辅存—主存—寄存器—Cache

D: 辅存—寄存器—主存—Cache

答案: 【 辅存—主存—Cache—寄存器】

11、单选题:

某一SRAM芯片,其容量为16K*8位,则其数据线和地址线的条数分别为___

选项:

A: 地址线14根,数据线8根

B: 地址线16根,数据线8根

C: 地址线和数据线均为8根

D: 地址线和数据线均为14根

答案: 【 地址线14根,数据线8根】

12、单选题:

DRAM的刷新方式,是以____为单位进行的。

选项:

A: 行

B: 列

C: 行或者列

D: 存储单元

答案: 【 行】

13、单选题:

一般的虚拟存储器系统是由___两级存储器构成。

选项:

A: 主存—辅存

B: 缓存—主存

C: 缓存—辅存

D: 寄存器—缓存

答案: 【 主存—辅存】

14、单选题:

DRAM存储器主要通过___来存储信息。

选项:

A: 电容

B: 触发器

C: 磁介质

D: 寄存器

答案: 【 电容】

15、单选题:

计算机的存储系统采用分级方式主要是为了___

选项:

A: 解决容量、速度、价格三者之间的矛盾。

B: 方便程序设计人员编程

C: 方便计算机硬件扩展

D: 方便硬件更新换代

答案: 【 解决容量、速度、价格三者之间的矛盾。】

16、单选题:

下列关于主存存取速度说法错误的是

选项:

A: 存取周期(Memory Cycle Time)是指存储器进行连续两次独立的存储器操作所需的总时间

B: 存取时间又称为存储器的访问时间,是指启动一次存储器操作到完成该操作所需的全部时间

C: 存取时间分读出时间和写入时间两种

D: 通常存取周期大于存取时间

答案: 【 存取周期(Memory Cycle Time)是指存储器进行连续两次独立的存储器操作所需的总时间】

17、单选题:

随机存储器按其存储信息的原理不同,可以分为静态RAM和动态RAM两大类。

下图是静态RAM芯片Interl2114的外特征示意图。图中,A9~A0为地址输入端;I/01~I/O4为数据输入/输出端;CS为片选信号(低电平有效);WE为写允许信(低电平为写,高电平为读);Vcc为电源端;GND为接地端。

由Intel2114的外特征图,我们可知其存储容量为____

备案号:冀ICP备20010840号 2020-2099辉辉网络科技 All Rights Reserved